#### **Features**

- Fully Compliant to VAN Specification ISO/11519-3

- Handles All Specified Module Types

- Handles All Specified Message Types

- . Handles Retransmission of Frames on Contention and Errors

- 3 Separate Line Inputs with Automatic Diagnosis and Selection

- Normal or Pulsed (Optical and Radio Mode) Coding

- VAN Transfer Rate: 1 Mbit/s Maximum

- SPI/SCI Interface

- SPI Transfer Rate: 4 Mbit/s MaximumSCI Transfer Rate: 125 Kbit/s Maximum

- Idle and Sleep Modes

- 128 Bytes of General-purpose RAM

- 14 Identifier Registers with All Bits Individually Maskable

- 6-source Maskable Interrupt, Including an Interrupt-on-reset to Detect Glitches on the Reset Pin

- Integrated Crystal or Resonator Oscillator with Internal Baud Rate Generator and Buffered Clock Output

- Single +5V Power Supply

- 0.8 μm CMOS Technology

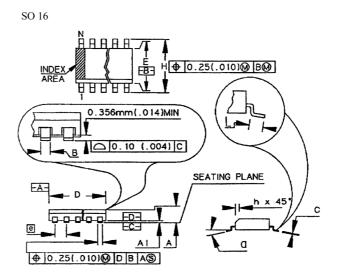

- SO16 Package

### **Description**

The TSS463AA is a circuit that allows the transfer of all the status information needed in a car or truck over a single low-cost wire pair, that minimizes electrical wire usage. It can be used to interconnect powerful functions to control and interface car body electronics (lights, wipers, power window, etc.).

The TSS463AA is fully compliant with the VAN ISO Standard 11519-3. This standard supports a wide range of applications such as low-cost remote-controlled switches. Typically it is used for lamp control, complex, highly-autonomous, distributed systems, which require fast and secure data transfers.

The TSS463AA is a microprocessor-interfaced line controller for mid- to high-complexity bus-masters and listeners like dashboard controllers, car stereo or mobile telephone CPUs.

The microprocessor interface consists of a 256-byte RAM and a register area divided into 11 control registers, 14 channel register sets and 128 bytes of general purpose RAM, used as a message storage area, and a 6-source maskable interrupt.

The circuit operates in the RAM using DMA techniques, controlled by the channel and control registers. This allows virtually any microprocessor, including SPI/SCI interface, to be connected easily to the TSS463AA.

Messages are encoded in enhanced Manchester code, and an optional pulsed code for use with an optical or radio link, at a maximum bit rate of 1 Mbit/s. The TSS463AA analyzes the messages received or transmitted according to 6 different criteria including some higher level checks.

In addition, the bus interface has three separate inputs with automatic source diagnosis and selection. The interface allows for multibus listening or the automatic selection of the most reliable source at any time if several line receivers are connected to the same bus.

# VAN Data Link Controller with Serial Interface

**TSS463-AA**

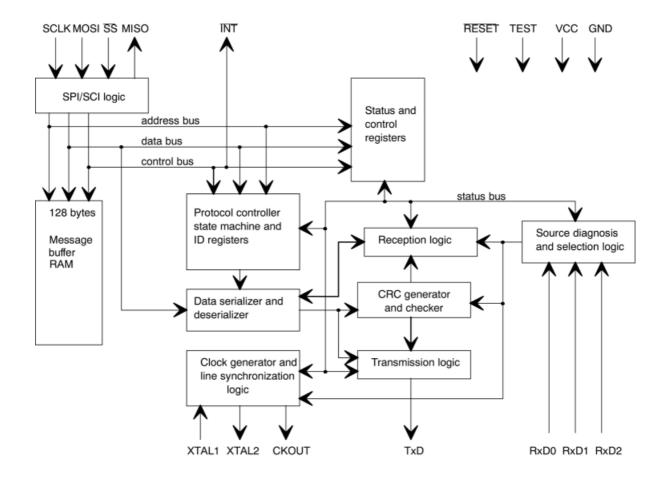

# **Block Diagram**

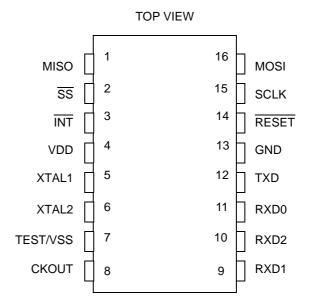

# **Pin Configuration**

# **Pin Description**

| I/O Type               | Pin Name | Pin No. | Pin Function                                           |

|------------------------|----------|---------|--------------------------------------------------------|

| O 3-state              | MISO     | 1       | SPI/SCI Data Output                                    |

| I trigger CMOS         | SS       | 2       | SPI/SCI Slave Select (active low)                      |

| Open-drain             | ĪNT      | 3       | Interrupt (active low)                                 |

| Power                  | VDD      | 4       | + 5V power supply                                      |

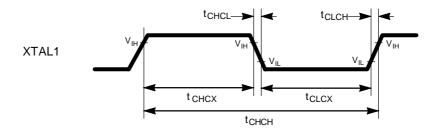

| I CMOS                 | XTAL1    | 5       | Crystal oscillator or clock input pin from 1 to 16 MHz |

| 0                      | XTAL2    | 6       | Crystal oscillator output pin                          |

| Ground                 | TEST/VSS | 7       | Test mode input                                        |

| 0                      | СКОИТ    | 8       | Buffered clock output                                  |

| I CMOS Pull-down       | RXD1     | 9       | VAN bus input 1                                        |

| I CMOS Pull-down       | RXD2     | 10      | VAN bus input 2                                        |

| I CMOS Pull-down       | RXD0     | 11      | VAN bus input 0                                        |

| O 3-state              | TXD      | 12      | VAN bus output                                         |

| Ground                 | GND      | 13      |                                                        |

| I trigger CMOS pull-up | RESET    | 14      | Hardware Reset (active low)                            |

| I trigger CMOS         | SCLK     | 15      | SPI/SCI Clock Input                                    |

| I trigger CMOS         | MOSI     | 16      | SPI/SCI Data Input                                     |

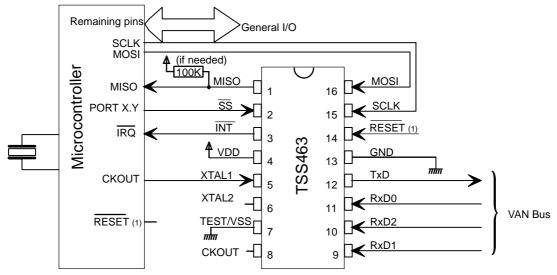

## **Application**

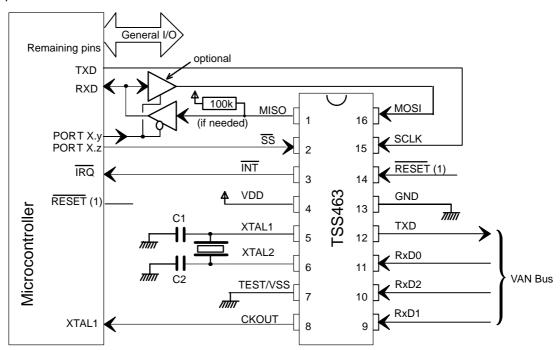

The TSS463AA is a microprocessor controlled line controller for the VAN bus. It can interface to virtually any microprocessor which includes SPI or SCI interface.

- The TSS463AA provides one full Motorola compatible SPI interface.

- It includes one full compatible Intel UART (mode 0 only).

- And finally, one 9-bits SCI interface is also integrated.

In addition, the circuit features a single interrupt pin. This pin can be treated as level sensitive. For example, if there is a pending interrupt inside the circuit when another interrupt is reset, the  $\overline{\text{INT}}$  pin will emit a high pulse with the same pulse width as the internal write strobe (typically 20 ns).

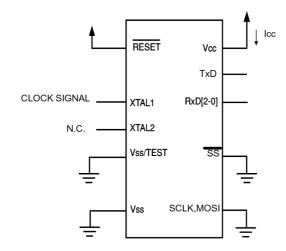

Figure 1. Typical Application With Motorola SPI Mode

Notes:

- 1. The TSS463AA RESET pin can either be connected to GND through a 1 μF capacitor, or the μC RESET pin or unconnected (inactive with internal pull-up).

- 2. Leaving MISO output pin floating in high impedance mode slightly increases standby consumption. A 100 K $\Omega$  pull-up/pull-down resistor is recommended.

## Microprocessor Interface

**Interface Modes**

Motorola SPI Mode

The processor controls the TSS463AA by reading and writing the internal registers of the circuit. These registers appear to the processor as regular memory locations.

The TSS463AA must be connected with an SPI or SCI serial interface. The following section provides information on switching from one mode to another.

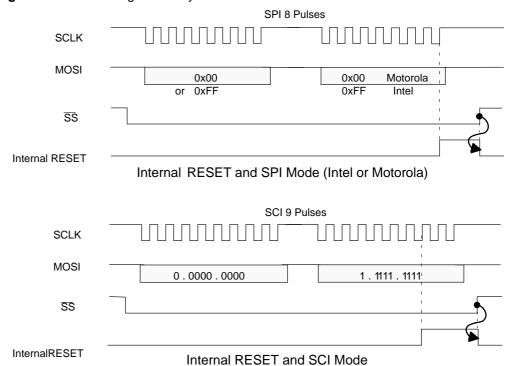

The first two bytes to be sent by the master (CPU) are called "Initialization Sequence": This sequence provides a proper asynchronous RESET in the TSS463AA and it selects the Motorola SPI, Intel SPI or the SCI serial mode. This initialization sequence is shown on Figure 4. Two 0x00 will cause an internal RESET and assert the Motorola SPI mode, Two "0xFF" will provide an internal RESET and assert the Intel<sup>®</sup> SPI mode and "9 bits to 0 followed by 0xFF or 0xFE" will generate an internal RESET and assert the 9-bits SCI mode.

Figure 2. Mode Configuration Byte

The Motorola Serial Peripheral Interface (SPI) is fully compatible with the SPI Motorola protocol. The interface is implemented for slave-mode only (the TSS463AA can not generate SPI frames by itself).

The SPI interface allows the interconnection of several CPUs and peripherals on the same printed circuit board.

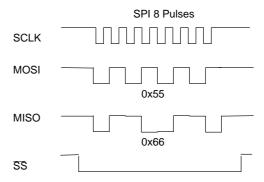

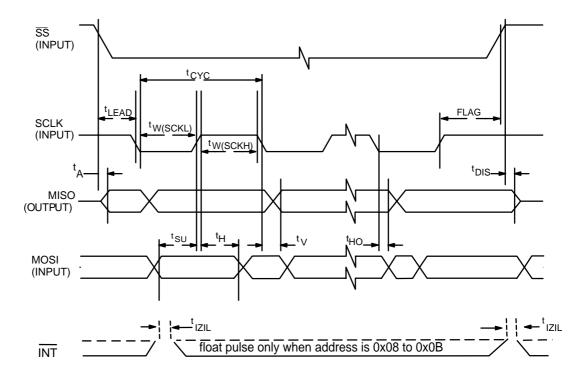

The SPI mode interface consists of 4 pins: separate wires are required for data and clock, so the clock is not included in the data stream as shown in Figure 5. One pin is needed for the serial clock (SCLK), two pins for data communication MOSI and MISO and one pin for Slave Select (SS).

Figure 3. SPI Data Stream

SCLK: Serial Clock

The master device provides the serial clock for the slave devices. Data is transferred synchronously with this clock in both directions. The master and the slave devices send/receive a data byte during an eight-clock pulse sequence.

MOSI: Master Out Slave In

The MOSI pin is the master device data output (CPU) and the slave device data input (TSS463AA). Data is transferred serially from the master to the slave on this line; most significant bit (MSB) first, least significant bit (LSB) last.

MISO: Master In Slave Out

The MISO pin is configured as the slave device data output (TSS463AA) and as master device data input (CPU). When the slave device is not selected ( $\overline{SS} = 1$ ), this pin is in high impedance state.

SS: Slave Select

The  $\overline{SS}$  pin is the slave chip select. It is low active. A low state on the Slave Select input allows the TSS463AA to accept data on the MOSI pin and send data on the MISO pin. The Slave Select signal must not toggle between each transmitted byte and should be left at a low level during the whole SPI frame.  $\overline{SS}$  must be asserted to inactive high level at the end of the SPI frame.

As mentioned before, if  $\overline{SS}$  is not asserted, MISO pin is in a high impedance state and incoming data is not driven to the serial data register.

SPI Protocol

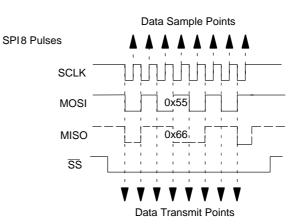

The general format of the data communication in the SPI frame between the TSS463AA and the host is a bit-for-bit exchange on each SCLK clock pulse. Data is arranged in the TSS463AA such that the significance of a bit is determined by its position from the start for output and from the end for input, most significant bit (MSB) is sent first. Bit exchanges in multiples of 8 bits are allowed.

The Idle Clock Polarity (CPOL) and the Clock Phase (CPHA) are not programmable: the CPOL and CPHA values to be programmed in the master (CPU) are CPOL = CPHA = 1. This is available for all modes. Waveforms with transmit and sample points are shown in Figure 6.

Figure 4. CPOL and CPHA in the TSS463AA

CPOL = CPHA = 1

At the beginning of a transmission over the serial interface, the first byte is the address of the TSS463AA register to be accessed. The next byte transmitted is the control byte which determines the direction of the communication. The following bytes are data bytes (consecutive bytes are written in or read from Address, Address + 1, Address + 2,..., Address + n with n = 0 to 28).

To make sure the TSS463AA is not out of synchronization, the SPI interface will transmit data "0xAA" and "0x55" on the MISO pin during address and control byte time. This way, the master always ensures the TSS463AA is well-synchronized. If the TSS463AA is out of synchronization, the master can assert the  $\overline{\rm SS}$  pin inactive to re synchronize the SPI interface or can assert the  $\overline{\rm RESET}$  pin active or can send an initialization sequence. When the  $\overline{\rm SS}$  pin is inactive, the SCLK is allowed to toggle. This will have no effect on the TSS463AA SPI module.

#### **SPI Control Byte**

The SPI control byte is transmitted by the master (CPU) to the TSS463AA. It specifies whether it is a TSS463AA Write or Read.

Table 1. SPI Control Byte

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| DIR | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

DIR: Serial Transfer Direction

Zero: Read Operation. The data bytes will be read by the master (CPU) from the TSS463AA.

One: Write Operation. The data bytes will be written by the master (CPU) to the TSS463AA.

In both cases, address auto-increment mechanism will take place when more than one data byte is read or written. This mechanism is inhibited when address value reaches 0xFF.

The seven following bits are reserved and must be equal to: 1100000.

When the master (CPU) conducts a write, it sends an address byte, a control byte and data bytes on its MOSI line. The slave device (TSS463AA) will send, if well-synchronized, "0xAA" during the address byte and "0x55" during the control byte on its MISO line.

When the master (CPU) conducts a read, it sends an address byte, a control byte and dummy characters ("0xFF" for instance) on its MOSI line. In the case of a VAN messages RAM read (VAN frame received), the first data byte sent back by the TSS463AA on its MISO pin is the *data length* so the master knows how many dummy characters it must send to read the VAN frame properly. When the TSS463AA responds back with data, it will not take care of the MOSI line.

The master must activate and de-activate  $\overline{SS}$  between each data frame.

Synchronization bytes must be monitored carefully. For instance, if "0xAA" and "0x55" are not monitored correctly, then the previous transmission may be incorrect too.

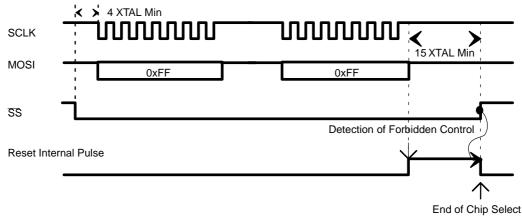

A control byte containing "0x00" or "0xFF" is forbidden except during an "Initialization Sequence".

#### **Intel SPI Mode**

The Intel SPI mode is the second type of interface. As mentioned before, the TSS463AA enters this mode if the Initialization Sequence contains (first two bytes received) "0xFF, 0xFF".

This mode is fully compatible to the Intel UART serial interface programmed in mode 0 only. It is the same as Motorola SPI mode (same CPOL and CPHA) but with inverted communication sense (LSB first and MSB last). The protocol is also the same.

However, from the master point of view (host microcontroller), the hardware is different. Figure 5 shows how to connect the TSS463AA and Intel type microcontroller.

Figure 5. Typical Application With the 8051 UART in Mode 0

Notes: 1. The RESET pin can either be connected to GND through a 1 µF capacitor, or the microcontroller RESET pin or unconnected (inactive with internal pull-up).

The master device provides the serial clock on the TxD pin and is still connected to SCLK pin of the slave device.

Then, the RxD replaces the MOSI and MISO pins and is a bi-directional pin. To achieve a correct communication, the user should add a few gates to connect the master RxD pin to the MOSI-MISO slave pins.

Figure 5 proposes two 3-state buffers controlled by the master through a general purpose I/O pin.

It is obvious that, in this Intel SPI mode, the master cannot monitor the "0xAA and 0x55" synchronization bytes while sending the address and control bytes. It is the only exception in this mode compared with the Motorola SPI mode.

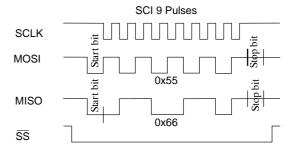

The SCI mode is the third type of interface. The TSS463AA enters this mode if the Initialization Sequence contains (first two bytes received) "0x00, 0xFF".

The SCI is compatible with a 9-bits SCI protocol. The interface is implemented for slave-mode only (the TSS463AA cannot generate SCI frames by itself).

The SCI interface allows an interconnection of several CPUs and peripherals on the same printed circuit board.

The SCI mode interface consists of 4 pins: separate wires are required for data and clock, so the clock is not included in the data stream as shown in Figure 6. One pin is needed for the serial clock (SCLK), two pins for data exchange MOSI and MISO and one pin for Slave Select SS.

Figure 6. SCI Data Stream

SCLK: Serial Clock

**SCI Mode**

The master device provides the serial clock for the slave devices. Data is transferred synchronously with this clock in both directions. The master and the slave devices exchange a data byte during a **nine** clock pulses sequence. However, the TSS463AA will only monitor 8 bits on its MOSI line and send 9 bits on its MISO line.

MOSI: Master Out Slave In

The MOSI pin is the master device data output (CPU) and the slave device data input (TSS463AA). Data is transferred serially from the master to the slave on this line; **least** significant bit (LSB) first, **most** significant bit (MSB) last. The TSS463AA will only monitor 8 bits starting from the LSB to MSB-1.

MISO: Master In Slave Out

The MISO pin is configured as the slave device data output (TSS4 $\underline{63}$ AA) and as master device data input (CPU). When the slave device is not selected ( $\overline{SS} = 1$ ), this pin is in high impedance state. The value of the MSB ( $9^{th}$  bit) sent on the MISO pin will always be "1" and should not be used by the master.

SS: Slave Select

The SS pin is the slave chip select. It is low active. A low state on the Slave Select input allows the TSS463AA to accept data on the MOSI pin and send data on the MISO pin.

The Slave Select signal must not toggle between each <u>transmitted</u> byte and therefore, should be left at a low level during the whole SCI frame. SS must be asserted to inactive high level at the end of the SCI frame.

If SS is not asserted, MISO pin is in high impedance state and incoming data is not driven to the serial data register.

**SCI Protocol**

Same as the SPI protocol described earlier except for data arranging (LSB first and MSB last).

Only 8 bits are monitored by the TSS463AA and master must monitor the 8 first bits too (9<sup>th</sup> bit always equal to 1).

**SCI Control Byte**

Same as the SPI control byte.

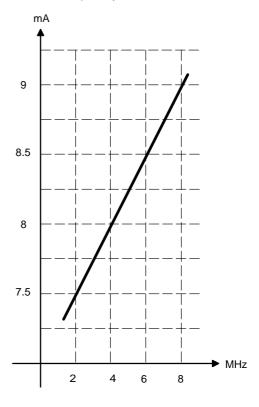

# Clocks and Speed Considerations

**SCLK and XTAL Clocks**

The SPI/SCI speed rate is given by the CPU producing SCLK. XTAL clock controls the speed rate on the VAN bus. The two clocks are asynchronous, but a minimum SPI/SCI interframe spacing must be apply according to XTAL clock.

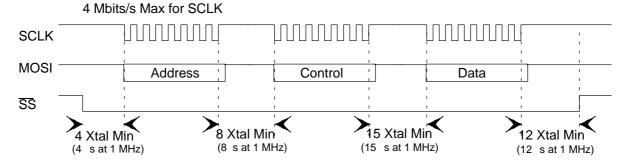

Intel and Motorola SPI Modes

Within an SPI byte, the maximum speed allowed on the MOSI line is 4 Mbits/s.

For example, when using a 1 MHz oscillator (sufficient to provide 62.5 kTS/s on the VAN bus) the minimum inter-character delay is 12  $\mu$ s (12 oscillator periods). Speed considerations are detailed in Figure 7.

Figure 7. SPI Speed Considerations

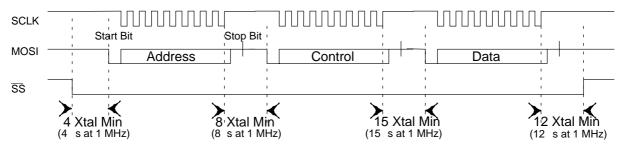

**SCI Mode**

Within an SCI 9-bits data, the maximum speed allowed on the MOSI line is 125 Kbits/s. When using a 1 MHz oscillator, the data transfer speed and the minimum delay time between SCI bytes are shown on Figure 8.

Figure 8. SCI Speed Considerations

#### 125 Kbits/s Max for SCLK

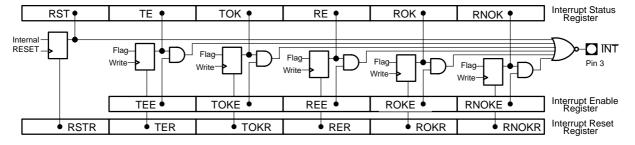

#### Interrupts

If an event occurs in the TSS463AA that needs the attention of the processor, this will be signalled on the active low, open-drain interrupt request pin. The event that creates this request is controlled by the internal registers.

Every time the microprocessor accesses any of the interrupt registers (addresses 0x08 to 0x0B), the INT pin will be released momentarily. This enables the TSS463AA to work with processors that have either edge or level sensitive interrupt inputs.

#### Reset

The reset is applied asynchronously or synchronously to the XTAL clock.

#### **Asynchronous Reset**

It can be done either by the RESET pin (hardware asynchronous reset) or by software (software asynchronous reset).

The RESET pin is a CMOS trigger input with a pull-up resistor ( $\sim 70 \text{ k}\Omega$ ). An external 1  $\mu\text{F}$  capacitor to GND provides to RESET pin an efficient behavior.

The asynchronous software reset is made by the "Initialization Sequence" described in "Motorola SPI Mode" on page 5.

Two "0x00" bytes provide an asynchronous software reset and configure the TSS463AA in the Motorola SPI mode while two "0xFF" bytes provide a reset and configure the component in the Intel SPI mode and "0x00 followed by 0xFF" provide a reset and configure the component in the SCI mode. The SS pin must be asserted as shown on Figure 9. The SPI/SCI logic will monitor these two bytes and provide an internal reset pulse asserting the TSS463AA in the right mode.

#### **Synchronous Reset**

A synchronous reset (regarding XTAL clock) is available on the TSS463AA during current operation. It is made through the GRES command bit of the Command Register (address 0x03).

The two kinds of reset are ordered and filtered. Then the internal reset, always asserted asynchronously, enables the internal oscillator. Then it waits for 12 clock periods and the oscillator stability.

The different blocks of the TSS463AA need to be turned on synchronously. The release of the internal reset is synchronous and a loose of clock can let the TSS463AA in permanent reset after applying Reset.

It is important to note that even after a reset on the RESET pin, the user should wait for 12 clock periods before sending the "Initialization Sequence" in order to select the SPI or SCI mode (because the default mode after a hardware reset is the Motorola SPI mode).

Figure 9. Asynchronous Software Reset with UART Intel Mode

### **Oscillator**

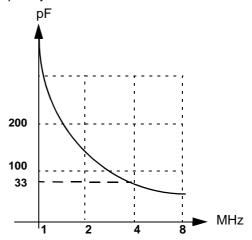

An oscillator is integrated in the TSS463AA, and consists of an inverting amplifier of which the input is XTAL1 and the output XTAL2.

A parallel resonance quartz crystal or ceramic resonator must be connected to these pins. As shown in Figure 5, two capacitors have to be connected from the crystal pins to ground. The values of C2 depend on the frequency chosen and can be selected using the schematic given in Figure 39.

If the oscillator is not used, then a clock signal must be fed to the circuit via the XTAL1 input.

Note that this pin will behave as a CMOS level compatible Schmitt trigger input.

In this case the XTAL2 output should be left unconnected. The oscillator also features a buffered clock output pin CKOUT. The signal on this pin is directly buffered from the XTAL1 input, without inversion.

There is one more pin used for the oscillator. The TEST/VSS pin is in fact its ground, and unless this pin is firmly connected to ground, with decoupling capacitors, the oscillator will not operate correctly.

The test mode itself, i.e., when the TEST/VSS pin is held high, is only intended for factory use, and the functionality of this mode is not specified in any way.

The TEST/VSS pin is subject to change without notice, the only exception is for incoming inspection tests using the test program.

The clock signal is then fed to the clock generator that generates all the necessary timing signals for the operation of the circuit. The clock generator is controlled by a 4-bit code called the clock divider.

$$f(TSCLK) = \frac{f(XTAL1)}{n \times 16}$$

Table 2. Clock Divider

| Clock   |           | 8 N     | lHz     | 6 M     | Hz      | 4 M     | Hz      | 2 MHz   |         |

|---------|-----------|---------|---------|---------|---------|---------|---------|---------|---------|

| Divider | Divide by | KTS/s   | Kbits/s | KTS/s   | Kbits/s | KTS/s   | Kbits/s | KTS/s   | Kbits/s |

| 0000    | 1         | 500     | 400     | 375     | 300     | 250     | 200     | 125     | 100     |

| 0001    | 2         | 250     | 200     | 187.50  | 150     | 125     | 100     | 62.50   | 50      |

| 0010    | 4         | 125     | 100     | 93.75   | 75      | 62.50   | 50      | 31.25   | 25      |

| 0011    | 8         | 62.5    | 50      | 46.875+ | 37.5    | 31.25   | 25      | 15.625  | 12.5    |

| 0100    | 16        | 31.25   | 25      | 23.438  | 18.75   | 15.625  | 12.5    | 7.813   | 6.25    |

| 0101    | 32        | 15.625  | 12.5    | 11.718  | 9.375   | 7.813   | 6.25    | 3.906   | 3.125   |

| 0110    | 64        | 7.813   | 6.25    | 5.859   | 4.688   | 3.906   | 3.125   | 1.953   | 1.562   |

| 0111    | 128       | 3.906   | 3.125   | 500     | 400     | 1.953   | 1.562   | 166.666 | 133.333 |

| 1000    | 1.5       | 333.333 | 266.666 | 250     | 200     | 166.666 | 133.333 | 83.333  | 66.666  |

| 1001    | 3         | 166.666 | 133.333 | 125     | 100     | 83.333  | 66.666  | 41.666  | 33.333  |

| 1010    | 6         | 83.333  | 66.666  | 62.50   | 50      | 41.666  | 33.333  | 20.833  | 16.666  |

| 1011    | 12        | 41.666  | 33.333  | 31.25   | 25      | 20.833  | 16.666  | 10.416  | 8.333   |

| 1100    | 24        | 20.833  | 16.666  | 15.625  | 12.50   | 10.416  | 8.333   | 5.208   | 4.166   |

| 1101    | 48        | 10.416  | 8.333   | 7.813   | 6.25    | 5.208   | 4.166   | 2.604   | 2.083   |

| 1110    | 96        | 5.208   | 4.166   | 3.906   | 3.125   | 2.604   | 2.083   | 1.302   | 1.042   |

| 1111    | 192       | 2.604   | 2.083   | 1.953   | 1.5625  | 1.302   | 1.042   | 0.651   | 0.521   |

#### VAN Protocol

#### Line Interface

There are three line inputs and one line output available on the TSS463AA. Which of the three inputs to use is either programmable by software or automatically selected by a diagnosis system.

The diagnosis system continuously monitors the data received through the three inputs, and compares it with each other and the selected bitrate. It then chooses the most reliable input according to the results.

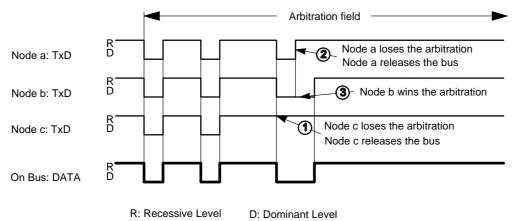

The data on the line is encoded according to the VAN standard ISO/11519-3. This means that the TSS463AA is using a two level signal having a recessive (1) and a dominant (0) state. Furthermore, due to the simple medium used, all data transmitted on the bus is also received simultaneously.

The VAN protocol is hence a CSMA/CD (Carrier Sense Multiple Access Collision Detection) protocol, allowing for continuous bitwise arbitration of the bus, and non-destructive (for the higher priority messa ge) collision detection.

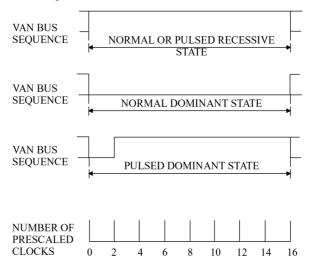

Figure 10. CSMA/CD Arbritration

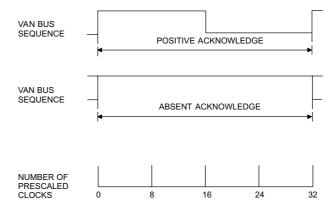

In addition to the VAN specification there is also a pulsed coding of the dominant and recessive states. This mode is intended to be used with an optical or radio link. In this mode, the dominant state for the transmitter is a low pulse, (2x prescaled clocks at the beginning of the bit) and the recessive state is just a high level. When receiving in this mode, it is not the state of the signal itself which is decoded, but the edges. Also, reception is imposed on the RxD0 input, and the diagnosis system does not operate correctly.

In addition, in this mode there is an internal loopback in the circuit since optical transceivers are not able to receive the signal that they transmit.

In Figure 11 the pulsed waveforms are shown. In Figure 14 through Figure 20 the low "timeslots" (i.e. blocks of 16 prescaled clocks) should be replaced by the dominant waveform showed in Figure 11 if the correct representations for pulsed coding are to be seen.

Figure 11. State Encoding

#### **VAN Frame**

Figure 12. VAN Bus Frame

| SOF | Identifier | Command |     |     |     | Data  | Frame<br>Check | EOD | ACK | EOF |

|-----|------------|---------|-----|-----|-----|-------|----------------|-----|-----|-----|

| 30F | Field      | EXT     | RAK | R/W | RTR | Field | Sum            | EOD | ACK | EOF |

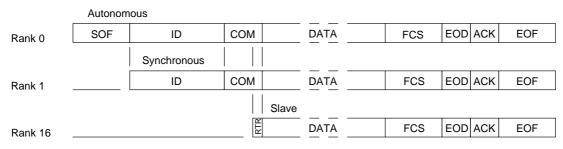

The VAN bus supports three different module (unit) types:

- 1. The *Autonomous* module, which is a bus master. It can transmit Start Of Frame (SOF) sequences, it can initiate data transfers and can receive messages.

- 2. The *Synchronous access* module. It cannot transmit SOF sequences, but it can initiate data transfers and can receive messages.

- 3. The *Slave* module, which can only transmit using an in-frame mechanism and can receive messages.

Figure 13. Hierarchical Access Methods

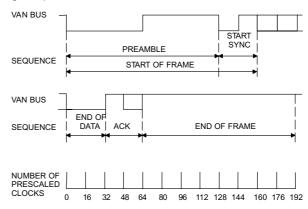

Figure 12 shows a normal VAN bus frame. It is initiated with a Start of Frame (SOF) sequence shown in Figure 14. The SOF can only be transmitted by an autonomous module. During the preamble, the TSS463AA will synchronize its bit rate clock to the data received.

Figure 14. Framing Sequences

When the complete SOF sequence has been transmitted or received, the circuit will start the transmission or reception of the identifier field.

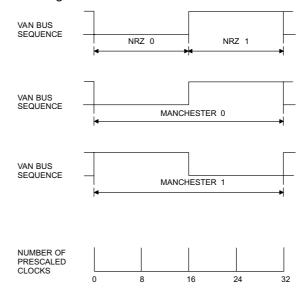

All data on the VAN bus, including the identifier and Frame Check Sum (FCS), are transmitted using enhanced Manchester code.

In enhanced Manchester code, three NRZ bits are transmitted first followed by one Manchester bit, then three more NRZ bits followed by one Manchester bit and so on.

Since the high state is recessive and the low state is dominant, the bus arbitration can be done. If a module wants access to the bus, it must first listen to the bus during one full End of Frame (EOF) and one full Inter Frame Spacing (IFS) period to determine whether the bus is free or not (i.e. no dominant states received).

Figure 15. Data Encoding

The IFS is defined to be a minimum of 64 prescaled clock periods. The TSS463AA, accepts an IFS of zero prescaled clocks for the reception only of a SOF sequence.

Once the bus has been determined as being free, the module must, if it is an autonomous module, emit an SOF sequence or, if it is a synchronous access module, wait until it detects a preamble sequence.

At this point there could be several modules transmitting on the bus, and there is no possibility of knowing if this is the case or not. Therefore, the first field in which arbitra-

tion can be performed is the identifier field. Since the logical zeroes on the bus are dominant, and all data is transmitted with the most significant bit (MSB) first, the first module to transmit a logical zero on the bus will be the prioritized module, i.e. the message that is tagged with the lowest identifier will have priority over the other messages.

It is possible that two messages transmitted on the bus will have the same identifier. The TSS463AA, therefore, continues the arbitration of the bus throughout the whole frame. Moreover, if the identifier in transmission has been programmed for reception as well, it transmits and receives messages simultaneously, right up until the Frame Check Sequence (FCS). Only then, if the TSS463AA has transmitted the whole message, it discard the message received. Arbitration loss in the FCS field is considered as a CRC error during transmission.

This feature is called full data field arbitration, and it enables the user to extend the identifier. For instance it can be used to transmit the emitting modules address in the first bytes of the data field, thus enabling the identifier to specify the contents of the frame and the data field to specify the source of the information.

The identifier field of the VAN bus frame is always 12 bits long, and it is always followed by the 4-bit command field:

- The first bit of the command is the extension bit (EXT). This bit is defined by the

user on transmission and is received and retained by the TSS463AA. To conform

with the standard it should be set to 1 (recessive) by the user, else the frame is

ignored without any IT generation.

- The second bit is the request ACKnowledge bit (RAK). If this bit is a logical one, the

receiving module must acknowledge the transfer with an in-frame

acknowledgement in the ACK field. If it is set to logical zero, then the ACK field must

contain an acknowledge absent sequence.

- The third bit is the Read/Write (R/W). This bit indicates the direction of the data in a frame.

- If set to zero, it is a "write" message, i.e., data transmitted by one module to be received by another module.

- If it is set to one, it implies a "read" message, i.e. a request that another module should transmit data to be received by the one that requested the data (reply request message).

- Last in the command field is the Remote Transmission Request bit (RTR). This bit is

a logical zero if the frame contains data and a logical one if the frame does not

contain data. In order to conform with the standard, a received frame includes the

combination R/W. RTR = 01 is ignored without any IT generation.

All the bits in the command field are automatically handled by the TSS463AA, so the user need not to be concerned for encoding and decoding of these bits. The command bits transmitted on the VAN bus are calculated from the current status of the active message.

The data field comes after the command field. This is just a sequence of bytes transmitted MSB first. In the VAN standard the maximum message length is set to 28 bytes, but the TSS463AA handles messages up to 30 bytes.

The next field is the FCS field. This field is a 15 bit CRC checksum defined by the following generator polynomial g(x) of order 15:

$$q(x) = x^{15} + x^{11} + x^{10} + x^9 + x^8 + x^7 + x^4 + x^3 + x^2 + 1$$

The division is done with a rest initialized to 0x7FFF, and an inversion of the CRC bits is performed before transmission.

However, since the CRC is calculated automatically from the identifier, command and data fields by the TSS463AA, therefore, the user should not be concerned with the circuit. When the frame check sequence has been transmitted, the transmitting module must transmit an End of Data (EOD) sequence, followed by the ACKnowledge field (ACK) and the End of Frame sequence (EOF) to terminate the transfer.

Figure 16. Acknowledge Sequences

### Frame Examples

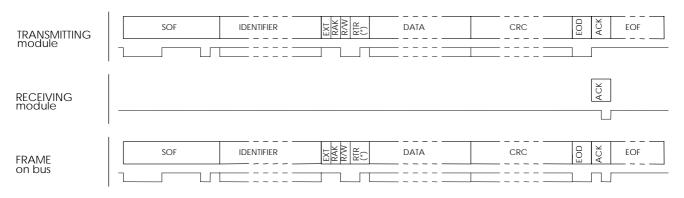

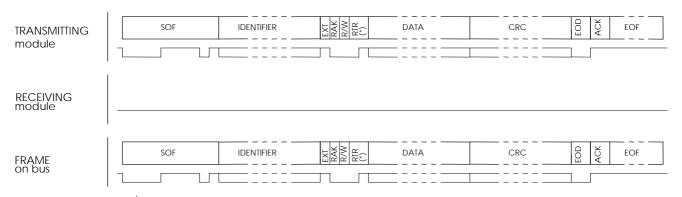

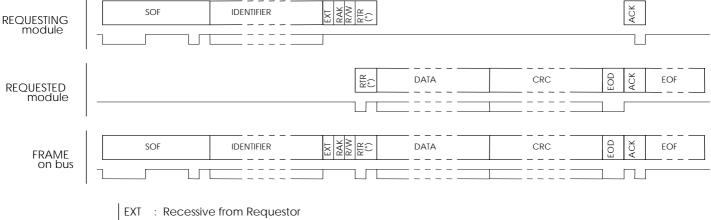

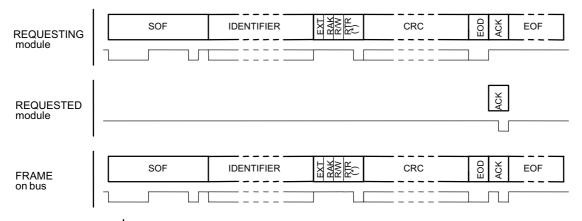

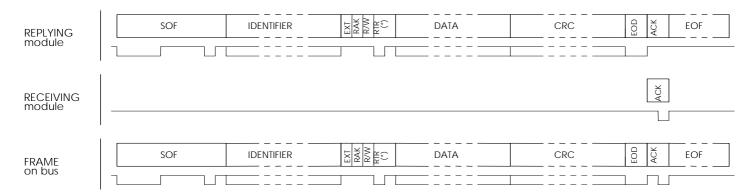

The frames transmitted on the VAN bus are generated by several modules, each supplying different parts of the message. Figure 17 through Figure 20 show the four frame types specified in the VAN standard, and the module that is generating the different fields.

The most straightforward frame is the normal data frame in Figure 17. Like all other frames, it is initiated with a SOF sequence. This sequence is generated by a bus master (not shown in the figure).

During this frame, there is basically only one module transmitting with the exception of the acknowledgement, generated by the receiving module if requested in the RAK bit.

• The reply request frame with immediate reply in Figure 18 is the only frame in which a slave module can transmit data by filling it into the appropriate field.

The only difference for the frame on the bus is that the R/W bit has changed state compared to the normal frame.

This is a highly interactive frame where a bus master generates the SOF and the initiator generates the identifier, the three first bits of the command, and the acknowledge. The RTR bit, the data field, the frame check, the EOD and the EOF are all generated by the replying module.

The reply request frame with deferred reply in Figure 19 is basically the same frame

as the reply request frame with immediate reply, but since the requested module

does not generate the RTR bit the requesting module will continue with the frame

check, the EOD and the EOF.

During this frame, the requested module will only generate the acknowledge, and only if this was requested by the initiator through the RAK bit.

• Finally, the deferred reply frame in Figure 20 which is sent when a module has prepared a reply for a reply request that has been received earlier.

This frame very closely mimics the normal data frame with the exception is the R/W bit that has changed state.

Figure 17. Normal Data Frame

With acknowledgment

EXT : Recessive from Transmitter

RAK: Recessive for acknowledge from Transmitter

R/W: Dominant from Transmitter

RTR: Dominant from Transmittet) Manchester bit ACK: Positive from Receiver because RAK is Recessive

#### Without acknowledgment

EXT : Recessive from Transmitter

RAK: Dominant for no acknowledge from Transmitter

R/W: Dominant from Transmitter

RTR : Dominant from Transmittet) Manchester bit

ACK: Absent from Transmitter and from Receiver because RAK is Dominant

Figure 18. Reply Request Frame with Immediate Reply

RAK: Recessive for acknowledge from Requestor

R/W: Recessive from Requestor

RTR : Recessive from Requestor and Dominant from Request@Manchester bit ACK: Absent from Requestee and Positive from Requestor because RAK is Recessive

Figure 19. Reply Request Frame with Deferred Reply

EXT: Recessive from Requestor

RAK: Recessive for acknowledge from Requestor

R/W: Recessive from Requestor

RTR: Recessive from Requestor - (\*) Manchester bit

ACK: Absent from Requestor and Positive from Requestee because RAK is Recessive

Figure 20. Deferred Reply Frame

EXT RAK R/W RTR

Recessive from Replyer Recessive for acknowledge from Replyer Recessive from Replyer Dominant from Replyer - (\*) Manches - (\*) Manchester bit

ACK: Absent from Replyer and Positive from Receiver because RAK is Recessive

## **Diagnosis System**

The purpose of the diagnosis system is to detect any short or open circuits on either the DATA or DATA lines and to permit, if it is possible, to carry the communications on the non-defective line.

The diagnosis system is based on the assumption that three separate line receivers are connected to the VAN bus see Figure 1:

- One of the line receivers is connected in differential mode, sensing both DATA and DATA signals, and is connected to the RxD0 input.

- The other two line receivers are operating in single wire mode and are sensing only one of the two VAN bus signals:

- The line receiver sensing DATA is connected to RxD1

- The line receiver sensing DATA is connected to RxD2

The diagnosis system analyzes and compares the data sent over both VAN lines. So, the diagnosis system executes a digital filtering and transition analyses. In order to perform its investigation, three internal signals are generated, RI (*Return to Idle*), SDC (*Synchronous Diagnosis Clock*) and TIP (*Transmission In Progress*).

One of four operating modes can be chosen to manage the results of the diagnosis system.

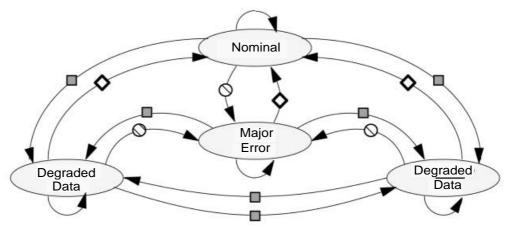

### **Diagnosis States**

If the diagnosis system finds a failure on any of the VAN bus signals, it changes from nominal to degraded mode, and connects the line receiver not coupled to the failing signal to the reception logic.

When the diagnosis system finds that the failing signal is working again, it returns to nominal mode and re-connects the differential line receiver to the reception logic.

A major error occurs when both the VAN bus signals failed.

Figure 21. Diagnosis States

- Failure during the frame

- Default of transitions on the valid input between 2 consecutive SDC rising edges.

- Protocol fault

- -In specified selection mode, every RI pulse when an EOF is detected or through an active SDC.

- -In automatic selection mode and SDC active, no failuresampled by 2 consecutive SDC rising edges.

- -General Reset

Status bits give permanent information on the diagnosis performed, whatever the programmed operating mode. This is encoded over three bits: Sa, Sb and Sc.

• Sa and Sb bits indicate the four possible states of the VAN bus.

Table 3. Status Bits: Sa and Sb

| Sa | Sb |        | Communication                                                                                               |

|----|----|--------|-------------------------------------------------------------------------------------------------------------|

|    |    | Mode   | Nominal                                                                                                     |

| 0  | 0  | Fault  | No fault on VAN bus                                                                                         |

|    |    | Status | Differential communication on DATA and DATA                                                                 |

|    |    | Mode   | Degraded on DATA                                                                                            |

| 0  | 1  | Fault  | Fault on DATA                                                                                               |

|    |    | Status | Communication on DATA                                                                                       |

|    |    | Mode   | Degraded on DATA                                                                                            |

| 1  | 0  | Fault  | Fault on DATA                                                                                               |

|    |    | Status | Communication on DATA                                                                                       |

|    |    | Mode   | Major error                                                                                                 |

| 1  | 1  | Fault  | Fault on DATA and DATA                                                                                      |

|    |    | Status | No communication on DATA and DATA (attempt to communicate alternatively on DATA then DATA every SDC period) |

Sc: As soon as one of the three inputs (RXD2, RXD1, RXD0) differs from the others in the input comparison analysis performed by the diagnosis system, Sc is set.

The only way to reset this status bit is through the RI signal or a general reset.

#### **Internal Operations**

### **Digital Filtering**

If several spurious pulses occur during one bit, the diagnosis for defective conductor may occur. To avoid such errors, digital filters are implemented.

Filtering operation is based on sampling of the comparator output signals. A transition is taken into account only if it is observed over five samples (1/16<sup>th</sup> of timeslot).

#### **Transition Analyses**

These analyses are continuously done on the effective edges on comparators after digital filtering.

### Asynchronous diagnosis

The <u>asynchronous</u> diagnosis is done by comparing the number of edges on DATA and DATA.

If four edges are detected on one input and no edges on the other during the same period, the second input is considered faulty and the diagnosis mode will change to one of the degraded modes.

#### Synchronous diagnosis

The synchronous diagnosis counts the number of edges on the data input connected to the reception logic during one SDC period.

If there are less than four edges during one SDC period, the diagnosis mode will change to the major error mode.

#### • Transmission diagnosis

The transmission compares RxD1 and RxD2 inputs (through the input comparators and the filters) with the data transmitted on TxD output.

At a time when the transmission logic generates a dominant - recessive transition, the inputs can give different values. Taking into account the filtering delay, the bus line seen as dominant is assumed to be correct, the other one, recessive, is considered faulty. The diagnosis mode is changed to reflect that.

#### Protocol fault

The protocol fault is detected by counting the number of consecutive dominant timeslots.

If eight consecutive timeslots are dominant, the diagnosis mode will change to the major error mode.

# Generation of Internal Signals

#### RI Signal (Return to Idle)

This signal is used to return to nominal mode in the three specified selection modes (see "Diagnosis States" on page 22 and "Programming Modes" on page 25). The RI signal is disabled in automatic selection mode.

The RI signal is a pulse generated when an EOF is detected. Thus, at the end of each frame, regarding the diagnosis status bit Sa, Sb and Sc, the user can make its own choice.

# SDC Signal (Synchronous Diagnosis Clock)

This time base is used by diagnosis system in automatic selection mode (see Section "Programming Modes", page 25) when no event is recorded on the bus.

The SDC is generated either by a special SDC divider connected to the timeslot clock, or can be performed manually. The SDC clock period must be long compared to the timeslot duration.

A typical SDC period should be greater than the maximum frame length appearing on the VAN network.

# TIP Signal (Transmission in Progress)

This signal must be enabled to allow the transmission diagnosis (see Section "Transition Analyses", page 23).

The TIP turns on synchronously with the beginning of the transmission:

- for asynchronous bus access, the beginning of SOF;

- for synchronous bus access, the beginning of the identifier field; and

- for a request of in frame reply, the RTR bit of the command field.

The TIP turns off synchronously with the end of the transmission:

- after EOF;

- · after a losing of arbitration or a code violation detection; and

- for a requestor of in frame reply, when the arbitration is lost on RTR the bit.

This signal is not generated when the transmission logic only sends an ACK.

# **Programming Modes**

Four programming modes determine how to use the three different inputs and the diagnosis system.

- 3 specified selection modes

- 1 automatic selection mode

Table 4. Programming Modes

| Ма | Mb                                      | Operating Mode                                     |  |

|----|-----------------------------------------|----------------------------------------------------|--|

| 0  | 0                                       | Differential communication                         |  |

| 0  | 1                                       | Degraded communication on RxD2 (DATA)              |  |

| 1  | 0 Degraded communication on RxD1 (DATA) |                                                    |  |

| 1  | 1                                       | Automatic selection according the diagnosis status |  |

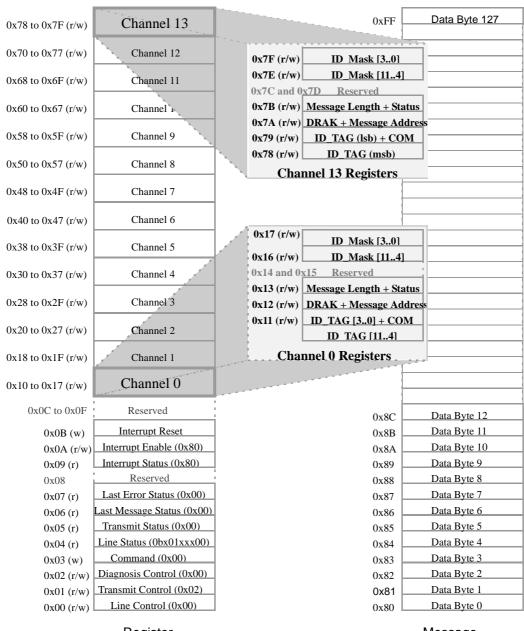

## **Registers**

The TSS463AA memory map consists of three different areas, the Control and Status registers, the Channel registers and the Message data (or Mailbox).

#### Mapping

Figure 22. Memory Map

Register Message

Notes: 1. All the non-specified addresses between 0x00 and 0x7F are considered as absent.

- (r) means read-only register.

- (w) means write-only register.

- (r/w) means read/write register.

- 3. Value after RESET is found after register name. If no value is given, the register is not initialized at RESET.

### **Control and Status Registers**

#### **Line Control Register (0x00)**

| 7   | 6   | 5   | 4   | 3  | 2 | 1    | 0    |

|-----|-----|-----|-----|----|---|------|------|

| CD3 | CD2 | CD1 | CD0 | PC | 0 | IVTX | IVRX |

- Read/write register.

- Default value after reset: 0×00

- Reserved: Bit 2, this bit must not be set by the user; a 0 must always be written to this bit.

CD[3:0]:Clock Divider

They control the VAN Bus rate through a Baud Rate generator according to the formula below:

$$f(TSCLK) = \frac{f(XTAL1)}{n \times 16}$$

PC: Pulsed Code

One: The TSS463AA will transmit and receive data using the pulsed coding mode (i.e optical or radio link mode). The use of this mode implies communication via the RxD0 input and the non-functionality of the diagnosis system.

Zero: (Default at reset). The TSS463AA will transmit and receive data using the Enhanced Manchester code. (RxD0, RxD1, RxD2 used).

IVTX: Invert TxD output IVRX: Invert RxD inputs

The user can invert the logical levels used on either the TxD output or the RxD inputs in order to adapt to different line drivers and receivers.

One: A one on either of these bits will invert the respective signals.

Zero: (Default at reset). The TSS463AA will set TxD to recessive state in Idle mode and consider the bus free (recessive states on RxD inputs).

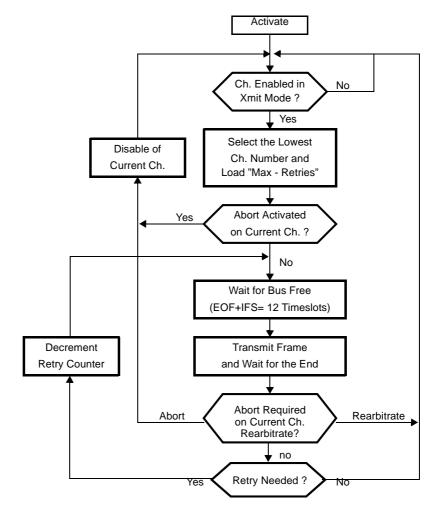

# Transmit Control Register (0x01)

| 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0  |

|-----|-----|-----|-----|------|------|------|----|

| MR3 | MR2 | MR1 | MR0 | VER2 | VER1 | VER0 | МТ |

Read/Write register.

Default value after reset: 0x02

MR[3:0]: Maximum Retries

These bits allow the user to control the amount of retries the circuit will perform if any errors occurred during transmission.

Table 5. Retries

| MR [3:0] | Max. # of retries | Max. # of transmissions |

|----------|-------------------|-------------------------|

| 0000     | 0                 | 1                       |

| 0001     | 1                 | 2                       |

| 0010     | 2                 | 3                       |

| 0011     | 3                 | 4                       |

| 0100     | 4                 | 5                       |

| 0101     | 5                 | 6                       |

| 0110     | 6                 | 7                       |

| 0111     | 7                 | 8                       |

| 1000     | 8                 | 9                       |

| 1001     | 9                 | 10                      |

| 1010     | 10                | 11                      |

| 1011     | 11                | 12                      |

| 1100     | 12                | 13                      |

| 1101     | 13                | 14                      |

| 1110     | 14                | 15                      |

| 1111     | 15                | 16                      |

Note: Bus contention is not regarded as an error and an infinite number of transmission attempts will be performed if bus contention occurs continuously.

VER[2:0] = 001

DLC Version after reset.

These bits must not be set by user. 001 must always be written to these bits.

MT: Module type

The three different module types are supported (see "VAN Frame" on page 15):

One: The TSS463AA is at once an autonomous module (Rank 0), a synchronous access module (Rank 1) or a slave module (Rank 16).

Zero: The TSS463AA is at once an synchronous access module (Rank 1) or a slave module (Rank 16).

#### **Diagnosis Control Register (0x02)**

| 7    | 6    | 5    | 4    | 3  | 2  | 1    | 0    |

|------|------|------|------|----|----|------|------|

| SDC3 | SDC2 | SDC1 | SDC0 | Ма | Mb | ETIP | ESDC |

- Read/Write register

- Default value after reset: 0×00.

The diagnosis is discussed in greater detail in the section "Diagnosis System" on page 22.

- In its four high order bits, the user can program the SDC rate SDC [3:0]

- In its two medium order bits, the diagnosis system mode is controlled: M1, M0.

- In the two low order bits, the user controls if the SDC and TIP are to be generated automatically ETIP, ESDC.

SDC [3:0]: SDC divider

The input clock is the timeslot clock.

Table 6. System Diagnosis Clock Divider

| SDC DIVIDER SDC [3:0] | Divide by |

|-----------------------|-----------|

| 0000                  | 64        |

| 0001                  | 128       |

| 0010                  | 256       |

| 0011                  | 512       |

| 0100                  | 1024      |

| 0101                  | 2048      |

| 0110                  | 4096      |

| 0111                  | 8192      |

| 1000                  | 16384     |

| 1001                  | 32768     |

| 1010                  | 65536     |

| 1011                  | 131072    |

| 1100                  | 262144    |

| 1101                  | 524288    |

| 1110                  | 1048576   |

| 1111                  | 2097152   |

SDC calculation: (see "SDC Signal (Synchronous Diagnosis Clock)" on page 24).

- Notes: 1. For each module, determine the largest interframe spacing, LIFS (\*).

- 2. For the whole network, get the maximum LIFS, MAX-LIFS.

- 3. SDC period > MAX-LIFS.

(\*) IFS min. = 4 TS

Example: For VAN frame speed rate = 62,5 KTS/s (1 TS = 16  $\mu$ s), SDC >100 ms => 100 ms / 16  $\mu$ s = 6250, divider chosen: 8192, SDC [3:0] = 0111.

# Ma, Mb: Operating Mode Command Bits

Table 7. Diagnosis System Command Bits

| Ма | Mb |                                                 |

|----|----|-------------------------------------------------|

| 0  | 0  | Forces the Communication on RxD0 (differential) |

| 0  | 1  | Forces the Communication on RxD2 (DATA)         |

| 1  | 0  | Forces the Communication on RxD1 (DATA)         |

| 1  | 1  | Automatic selection                             |

ETIP: Enable Transmission In Progress

The Transmission In Progress (TIP) tells the diagnosis system to enable transmission diagnosis.

One: Enable TIP generation Zero: Disable TIP generation.

ESDC: Enable System Diagnosis Clock The Synchronous Diagnosis Clock (SDC) controls the cycle time of the synchronous diagnosis.

One: Enable SDC divider. Zero: Disable SDC divider.

#### Command Register (0x03)

| 7    | 6     | 5    | 4    | 3    | 2 | 1 | 0    |

|------|-------|------|------|------|---|---|------|

| GRES | SLEEP | IDLE | ACTI | REAR | 0 | 0 | MSDC |

- Write only register.

- Reserved: Bit 1, 2 these bits must not be set by the user; a zero must always be written to these bit.

- If the circuit is operating at low bitrates there might be a considerable delay between the writing of this register and the performing of the actual command (worst case 6 timeslots). The user is therefore recommended to verify, by reading the Line Status Register (0x04), that the commands have been performed.

GRES: General Reset

The Reset circuit command bit performs, if set, exactly as if the external reset pin was asserted. This command bit has its own auto-reset circuitry.

One: Reset active Zero: Reset inactive

SLEEP: Sleep Command

(See Section "Sleep Command", page 52). If the user sets the Sleep bit, the circuit will enter sleep mode. When the circuit is in sleep mode, all non-user registers are setup to minimize power consumption. Read/write accesses to the TSS463AA via the SPI/SCI interface are impossible, the oscillator is stopped.

To exit from this mode the user must apply either an hardware reset (external RESET pin) or an asynchronous software reset (via the SPI/SCI interface).

One: Sleep active Zero: Sleep inactive

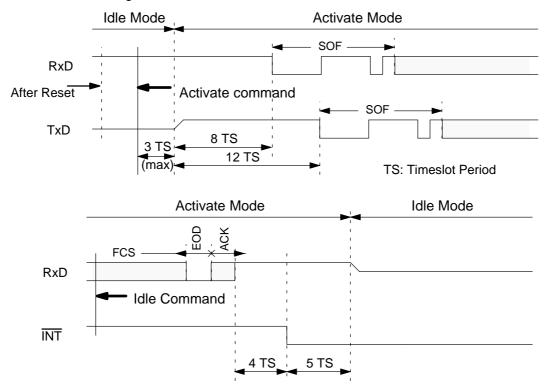

IDLE: Idle Command

(See Section "Idle and Activate Commands", page 52). If the user sets the Idle bit, the circuit will enter idle mode. In idle mode the oscillator will operate, but the TSS463AA will not transmit or receive anything on the bus, and the TxD output will be in three state.

One: Idle active Zero: Idle inactive

ACTI: Activate Command

(See Section "Idle and Activate Commands", page 52). The Activate command will put the circuit in the active mode, i.e it will transmit and receive normally on the bus. When the circuit is in activate mode the TxD three-state output is enabled.

One: Activate active Zero: Activate inactive

REAR: Re-Arbitrate Command

This command will, after the current attempt, reset the retry counter and re-arbitrate the messages to be transmitted in order to find the highest priority message to transmit.

One: Re-arbitrate active Zero: Re-arbitrate inactive

MSDC: Manual System Diagnosis Clock Rather than using the SDC divider described in Section "Message Data (string pointed by: Message Pointer Register + 1)", page 44, the user can use the manual SDC command to generate a SDC pulse for the diagnosis system.

This MSDC pulse should be high at least 2 timeslot clocks.

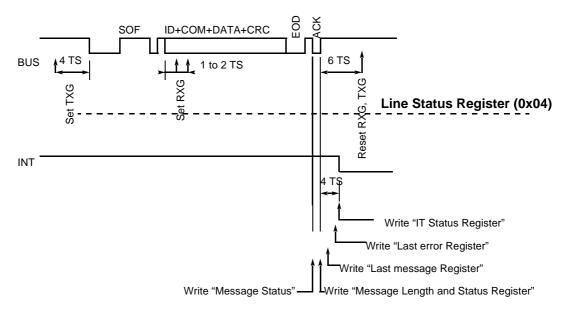

#### Line Status Register (0x04)

| 7 | 6   | 5   | 4  | 3  | 2  | 1   | 0   |

|---|-----|-----|----|----|----|-----|-----|

| Х | SPG | IDG | Sc | Sb | Sa | TXG | RXG |

- Read only register

- Default value after reset: 0bx01xxx00.

- This register reports the operation mode of the TSS463AA in the Sleep an Idle bits (Command Register located at address 0×03) as well as the diagnosis system status bits Sa to Sc discussed in the section "Diagnosis System" on page 22.

SPG: Sleeping

IDG: Idling

Default mode at reset

Sa, Sb and Sc: Diagnosis System Status Bits Sa and Sb

Diagnosis System Status Bits

| Sb | Sa | Communication Indication                 |  |  |  |  |

|----|----|------------------------------------------|--|--|--|--|

| 0  | 0  | Nominal mode, differential communication |  |  |  |  |

| 0  | 1  | Degraded over DATA, fault on DATA        |  |  |  |  |

| 1  | 0  | Degraded over DATA, fault on DATA        |  |  |  |  |

| 1  | 1  | Major error, fault on DATA and DATA      |  |  |  |  |

• **Sc:** As soon as one of the three inputs (RxD2, RxD1, RxD0) differs from the others in the input comparison analysis performed by the diagnosis system, Sc is set. The only ways to reset this status bits through the RI signal or a general reset.

TXG: Transmitting

If this status bit is active, it indicates that the TSS463AA has chosen an identifier to transmit, and it will continue to make transmission attempt for this message until it succeeds or the retry count is exceeded.

RXG: Receiving

The receiving indicates that there is activity on the bus.

*Note*: For safe modification of active channel registers both bits should be inactive (except "abort" command).

# Transmission Status Register (0x05)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| NRT3 | NRT2 | NRT1 | NRT0 | IDT3 | IDT2 | IDT1 | IDT0 |

- Read only register.

- Default value after reset: 0x00.

- The transmission Status register contains the number of retries made up-to-date, according to the table above, and the channel currently in transmission.

NRT [3:0]:

Number of retries done in transmission.

IDT [3:0]:

Channel number currently in transmission.

# Last Message Status Register (0x06)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| NRTR3 | NRTR2 | NRTR1 | NRTR0 | IDTR3 | IDTR2 | IDTR1 | IDTR0 |

- Read only register.

- Default value after reset: 0x00.

- This register is basically the same as the transmission status register. It contains the last identifier number that was successfully transmitted, received or exceeded its retry count.

If it was a successful transmission, the number of retries performed can be seen in this register as well.

NRTR [3:0]:

Number of retries done successfully in transmission. In case of reception NRTR[3:0] is undefined.

IDTR [3:0]:

Channel number that was successfully transmitted, received or exceeded its retry count.

#### **Last Error Status Register (0x07)**

| 7 | 6   | 5   | 4 | 3    | 2    | 1  | 0  |

|---|-----|-----|---|------|------|----|----|

| Х | вос | BOV | Х | FCSE | ACKE | CV | FV |

- Read only register.

- Default value after reset: 0×00.

- The Last Error Status Register contains the error code for the last transmission or reception attempt. It is updated after each attempt, i.e., several error codes can be reported during one single transmission (with several retries).

BOC: Buffer Occupied

- when one channel configured in "Reply request" mode has its "received" bit set when it attempts to transmit its request.

- BOC with the link capability between two channels sharing the same received buffer, is set when one channel has already set its "received" bit in its "Message length and status Channel register" and a receive is attempt on the other one.

One: BOC active Zero: BOC inactive

**BOV**: Buffer Overflow

BOV indicates that the buffer length setup in the Channel Status Register was shorter than the number of bytes received plus 1, and thus, some data was lost.

One: BOV active Zero: BOV inactive

FCSE: Framing Check Sequence Error FCSE indicates a mismatch between the FCS received and the FCS calculated

One: FCSE active Zero: FCSE inactive

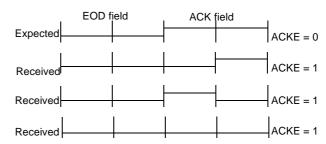

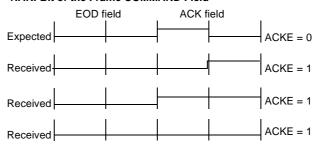

ACKE: Acknowledge Error

ACKE indicates a physical violation or collision on ACK field of the frame when the TSS463AA is a producer.

One: ACKE active Zero: ACKE inactive

Figure 23. ACKE Status bit

#### **DLC: Producer**

#### $RAK^* = 1$

#### \*RAK: Bit of the Frame COMMAND Field

#### CV: Code Violation

#### CV indicates:

- either a Manchester code violation (2 identical TS on Manchester bit), or a physical violation (transmitted bit "dominant", received bit "recessive"), on fields ID, COM, DATA and CRC.

- or a physical violation or collision on field "preamble" and the "recessive" bit of the "Star Sync" field.

One: CV active Zero: CV inactive

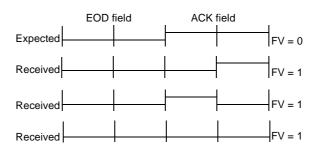

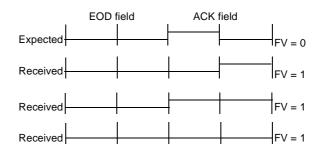

#### FV: Frame Violation

FV indicates a physical violation or collision on ACK field of the frame when the TSS463AA is a consumer.

One: FV active Zero: FV inactive

Figure 24. FV Status Bit

#### **DLC: Consumer**

### Interrupt Status Register (0x09)

| 7   | 6 | 5 | 4  | 3   | 2  | 1   | 0    |

|-----|---|---|----|-----|----|-----|------|

| RST | Х | Х | TE | ток | RE | ROK | RNOK |

- · Read only register.

- Default value after reset: 1xx0 0000

#### RST: Reset Interrupt

RE indicates that the circuit has detected a valid reset command via the  $\overline{\text{RESET}}$  pin or the reset command bit GRES. This interrupt cannot be disabled, since its enable bit is set when a reset is detected.

One: Status flag activated Zero: No status flag.

TE: Transmit Error Status Flag (or Exceeded Retry)

This flag is set only when the Max number of transmission (1 + MR [3:0]) is reached with error of transmission.

One: Status flag activated Zero: No status flag.

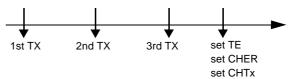

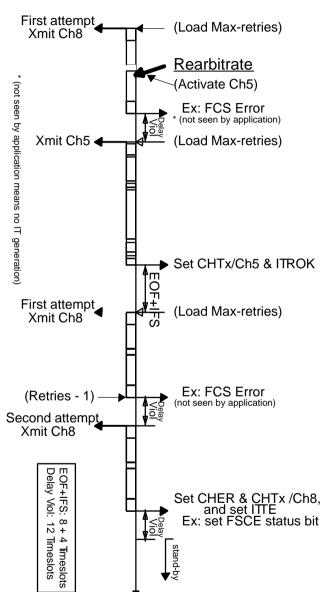

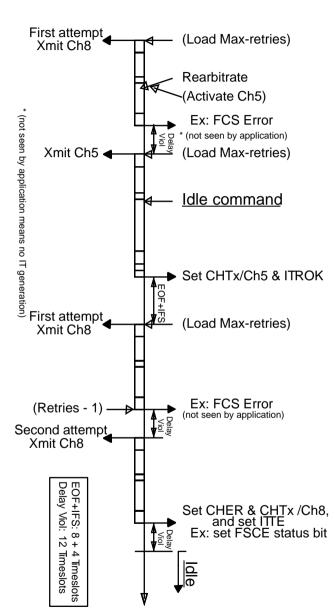

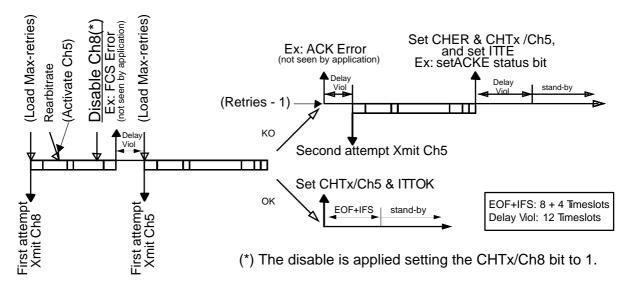

Figure 25. Exceeded Retry with MR[3..0] = 3

TOK: Transmit OK Status Flag One: Status flag activated

Zero: No status flag.

RE: Receive Error Status Flag One: Status flag activated

Zero: No status flag.

ROK: Receive "with RAK One (RAK=1)" OK Status Flag Zer

One: Status flag activated Zero: No status flag.

RNOK: Receive "with no RAK (RAK=0)" OK Status Flag

One: Status flag activated Zero: No status flag.

#### Interrupt Enable Register (0x0A)

| 7 | 6 | 5 | 4   | 3    | 2   | 1    | 0     |

|---|---|---|-----|------|-----|------|-------|

| 1 | х | х | TEE | TOKE | REE | ROKE | RNOKE |

Read/write register.

Default value reset: 1xx0 0000

Note: On reset the Reset Interrupt Enable bit is set to 1 instead of 0, as is the general rule.

TEE: Transmit Error Enable One: IT enabled.

Zero: IT disabled.

TOKE: Transmission OK Enable One: IT enabled.

Zero: IT disabled.

REE: Reception Error Enable One: IT enabled.

Zero: IT disabled.

ROKE: Reception "with RAK"

OK Enable

One: IT enabled. Zero: IT disabled.

RNOKE: Reception "with no

RAK" OK Enable

One: IT enabled. Zero: IT disabled.

#### Interrupt Reset Register (0x0B):

| 7    | 6 | 5 | 4   | 3    | 2   | 1    | 0     |

|------|---|---|-----|------|-----|------|-------|

| RSTR | 0 | 0 | TER | TOKR | RER | ROKR | RNOKR |

- Write only register.

- Reserved bit: 5 and 6. This bit must not be set by user; a zero must always be written to this bit.

RSTR: Reset Interrupt Reset One: Status flag reset.

Zero: Status flag unchanged.

TER: Transmit Error Status Flag

Reset

One: Status flag reset. Zero: Status flag unchanged.

TOKR: Transmit OK Status Flag

Reset

One: Status flag reset.

Zero: Status flag unchanged.

RER: Receive Error Status Flag

Reset

One: Status flag reset.

Zero: Status flag unchanged.

ROKR: Receive "with RAK" OK

Status Flag Reset

One: Status flag reset.

Zero: Status flag unchanged.

RNOKR: Receive "with no RAK"

OK Status Flag Reset

One: Status flag reset. Zero: Status flag unchanged.

Figure 26. Update of the Status Register

#### **Channel Registers**

There is a total of 14 channel register sets, each occupying 8 bytes for addressing simplicity, integrated into the circuit. Each set contains two 2  $\times$  8-bit registers for the identifier tag, identifier mask and command fields plus two 1  $\times$  8-bit registers for DMA pointers and message status.

The base\_address of each set is:

#### $(0x10 + [0x08 * channel_number]).$

When the TSS463AA is reset either via the external RESET pin or the general reset command, the channel registers are not affected. That is, on power-up of the circuit, all the channel registers start with random values.

Due to this fact, the user should take care to initialize all the channel registers before exiting from idle mode. The easiest way to disable a channel register is to set the received and transmitted bits to 1 in the Message Length and Status Register.

Table 8. Channel Register Sets Map

| Channel Number | from | to   | Channel Number | from | to   |

|----------------|------|------|----------------|------|------|

| 6              | 0x40 | 0x47 | 13             | 0x78 | 0x7F |

| 5              | 0x38 | 0x3F | 12             | 0x70 | 0x77 |

| 4              | 0x30 | 0x37 | 11             | 0x68 | 0x6F |

| 3              | 0x28 | 0x2F | 10             | 0x60 | 0x67 |

| 2              | 0x20 | 0x27 | 9              | 0x58 | 0x5F |

| 1              | 0x18 | 0x1F | 8              | 0x50 | 0x57 |

| 0              | 0x10 | 0x17 | 7              | 0x48 | 0x4F |

Table 9. Channel Register Set Structure

| Reg. Name      | Offset | Bit 7 | Bit 6       | Bit 5     | Bit 4 | Bit 3     | Bit 2 | Bit 1 | bit 0 |

|----------------|--------|-------|-------------|-----------|-------|-----------|-------|-------|-------|

| ID_MASK        | 0x07   |       | ID_M        | [3:0]     |       | х         | х     | х     | х     |

| ID_MASK        | 0x06   |       |             |           | ID_M  | [11:4]    |       |       |       |

| (No register)  | 0x05   | х     | х           | х         | х     | х         | х     | х     | х     |

| (No register)  | 0x04   | х     | х           | х         | х     | х         | х     | х     | х     |

| MESS_L/<br>STA | 0x03   |       |             | M_L [4:0] |       |           | CHER  | CHTx  | CHRx  |

| MESS_PTR       | 0x02   | DRACK |             |           |       | M_P [6:0] |       |       |       |

| ID_TAG/<br>CMD | 0x01   |       | ID_T [3: 0] |           |       |           | RAK   | RNW   | RTR   |

| ID_TAG         | 0x00   |       |             |           | ID_T  | [11:4]    |       |       |       |

### Identifier Tag and Command Registers

The identifier tag and command registers are located at the base\_address and base\_address + 1. It allows the user to specify the full 12-bit identifier field of the ISO standard and the 4-bit command.

| 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |                        |

|---------|---------|--------|--------|--------|--------|--------|--------|------------------------|

| ID_T 3  | ID_T 2  | ID_T 1 | ID_T 0 | EXT    | RAK    | RNW    | RTR    | base_address<br>+ 0x01 |

| 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |                        |

| ID_T 11 | ID_T 10 | ID_T 9 | ID_T 8 | ID_T 7 | ID_T 6 | ID_T 5 | ID_T 4 | base_address<br>+ 0x00 |

Read/Write registers.

ID\_T [11:0]: Identifier Tag

Upon a reception hit (i.e, a good comparison between the identifier received and an identifier specified, taking the comparison mask into account, as well as a status and command indicating a message to be received), the identifier tag bits value will be rewritten with the identifier bits actually received.

EXT, RAK, RNW and RTR

(See Section "Message Types", page 45). No comparison will be done on the command bits, except on EXT bit. The RAK, RNW and RTR bits will be written into the first byte of the Message upon a reception hit.

The RNW and RTR bits, as well as the status bits in the length and status register, must be in a valid position for reception or transmission. If not, the message corresponding to this identifier is considered as inactive or invalid.

The way of knowing if an acknowledge sequence was requested or not is to check the first byte of the Message.

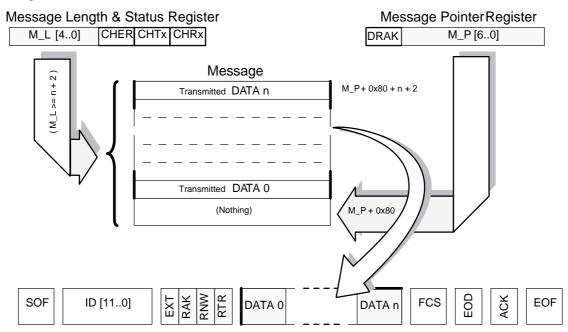

#### Message Pointer Register

The message pointer register at address (base\_address + 0x02) is 8 bits wide. It indicates where in the Message DATA RAM area the message buffer is located.

| /    | 6     | 5     | 4     | 3     | . 2   | 1     | 0     |                        |

|------|-------|-------|-------|-------|-------|-------|-------|------------------------|

| DRAK | M_P 6 | M_P 5 | M_P 4 | M_P 3 | M_P 2 | M_P 1 | M_P 0 | base_address<br>+ 0x02 |

· Read/Write register.

DRAK: Disable RAK (Used in 'Spy Mode')

In reception: whatever is the RAK bit of the incoming valid frame, no ACK answer will be set. If the message was successfully received, an IT is set (ROK or RNOK).

In transmission: no action.

One: disable active, "spy mode".

Zero: disable inactive, normal operation.

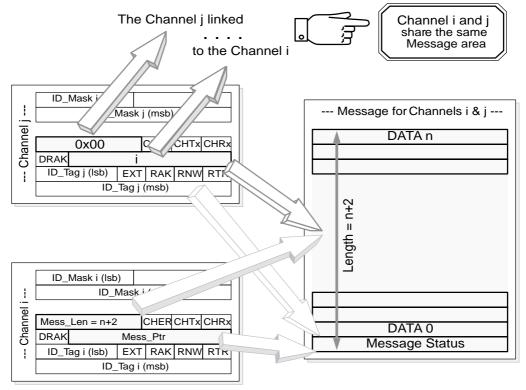

M\_P [6:0]: Message Pointer

Since the Message DATA RAM area base address is 0x80, the value in this register is the offset from that address. If the message buffer length value is illegal (i.e. zero), this register is redefined as being a link pointer, thus containing the channel number of the channel that contains the actual message pointer, message length and received status. However, the identifier, mask, error and transmitted status used will be that of the originally matched channel. In any case, if a link is intended, the three high bits of M\_P [6:0] should be set to 0.

This allows several channels to use the same actual reception buffer in Message DATA RAM, thus diminishing the memory usage.

Note: Only 1 level of link is supported.

#### Message Length And Status Register

The message length and status register at address (base\_address + 0x03) is also 8 bits wide. It indicates the length of reserved for the message in the Message DATA RAM area.

| 7   | 6     | 5     | 4     | 3     | 2    | 1    | 0    |                        |

|-----|-------|-------|-------|-------|------|------|------|------------------------|

| M_L | M_L 3 | M_L 2 | M_L 1 | M_L 0 | CHER | CHTx | CHRx | base_address<br>+ 0x03 |

Read/Write register.

#### M\_L [4:0]: Message Length

The 5 high bits of this register allows the user to specify either the length of the message to be transmitted, or the maximum length of a message receivable in the pointed reception buffer.

*Note:* The first byte in this register does not contain data, but the length of the message received. This implies that the length value has to be equal to or greater than the maximum length of a message to be received in this buffer (or the length of a message to be transmitted) plus 1, thus allowing a maximum length of 30 bytes and a minimum length of 0 byte.

If the value of this field is "illegal" (i.e 0x00) then this message pointer is defined as being a link (see Message pointer and register and "Linked Channels" on page 53).

| M_L [4:0] = 0x00 | Linked channel               |

|------------------|------------------------------|

| M_L [4:0] = 0x01 | Frame with no DATA field (*) |

| M_L [4:0] = 0x02 | Frame with 1 DATA byte       |

|                  |                              |

| M_L [4:0] = 0x1D | Frame with 28 DATA bytes     |

| M_L [4:0] = 0x1E | Frame with 29 DATA bytes     |

| M_L [4:0] = 0x1F | Frame with 30 DATA bytes     |

Note: Different of a reply request frame with no in-frame reply (deferred reply).

### CHER: Channel Error Status and Abort Command

As status, this bit is set by the TSS463AA when error occurs in transmission or on a received frame. The user must reset it.

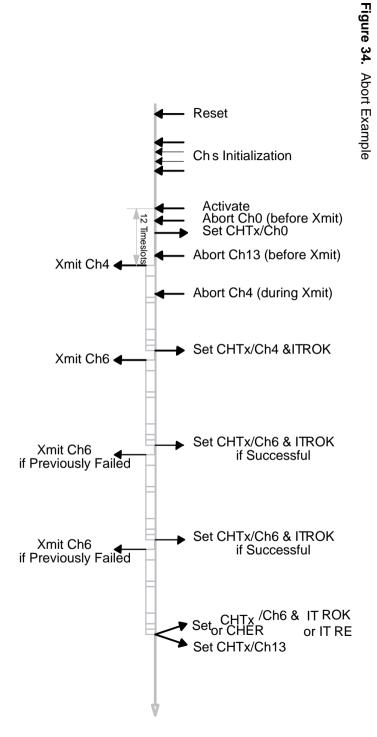

To abort the transmission defined in the channel, this bit can be set to 1 by the user (see Section "Activate, Idle and Sleep Modes", page 52 and "Abort" on page 50).

### CHTx: Channel Transmitted and Transmit Enable Command

CHRx: Channel Received and Receive Enable Command

The 2 low order bits of this register contain the message status. Together with the RNW and RTR bits of the command register (base\_address + 0x01), they define the message type of this channel (see section "Message Types" on page 45). As a general rule, the status bits are only set by the TSS463AA, so the user must reset them to perform a

transmission (CHTx) or/and a reception (CHRx). The received and transmitted bits are only set if the corresponding frame is without errors or if the retry count has been exceeded.

#### **Identifier Mask Registers**

The Identifier Mask registers (base\_address + 0x06 and base\_address + 0x07) allow bitwise masking of the comparison between the identifier received and the identifier specified.

| 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |                        |

|---------|---------|--------|--------|--------|--------|--------|--------|------------------------|

| ID_M 3  | ID_M 2  | ID_M 1 | ID_M 0 | х      | х      | х      | х      | base_address<br>+ 0x07 |

| 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |                        |

| ID_M 11 | ID_M 10 | ID_M 9 | ID_M 8 | ID_M 7 | ID_M 6 | ID_M 5 | ID_M 4 | base_address<br>+ 0x06 |

Read/Write registers.

ID\_M [11:0]: Identifier Mask

A value of 1 indicates comparison enabled. A value of 0 indicates comparison disabled.

#### Example:

- ID\_M[11:0] = 0x0FF8

- Acceptance: ID's from 0x0FF8 up to 0x0FFF

#### **Mailbox**

The mailbox contains all the messages received or to be transmitted. Each messages is link to a channel. The Mailbox RAM area has 128 bytes and is mapped from 0x80 to 0xFF (see Section "Mapping", page 26).

The message (or message buffer) is composed of:

- 1 byte of message status (only used in receiving),

- n bytes of data. These data are the bytes of the DATA field of the frame with the same organization.

The message is pointed by the Message Pointer Register of the channel, the length of the message is given by the Message Length and Status Register of the channel. This area is a pure RAM, it contains a random value after reset.

Figure 27. Message Buffer Structure for Reception

Received DATA Frame, immediate or deffered reply

Figure 28. Message Buffer Structure for Transmission

Transmitted DATA Frame

# Message Status (Pointed by: Message Pointer Register)

| 7    | 6    | 5    | 4     | 3     | 2     | 1     | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| RRAK | RRNW | RRTR | RM_L4 | RM_L3 | RM_L2 | RM_L1 | RM_L0 |

• (no significant value in case of message to be transmitted)

RRAK: Received RAK Bit This bit is the RAK bit coming from the COM field of the received frame.

RRNW: Received RNW Bit This bit is the RNW bit coming from the COM field of the received frame.

RRTR: Received RTR Bit This bit is the RTR bit coming from the COM field of the received frame.

$RM\_L[4:0]: Message\ Length\ of$  If the DATA field of the received frame included DATA0 to DATAn,  $RM\_L[4:0] = n+1$ , the Received Frame even if the reserved length (Message Length and Status Register) is larger.

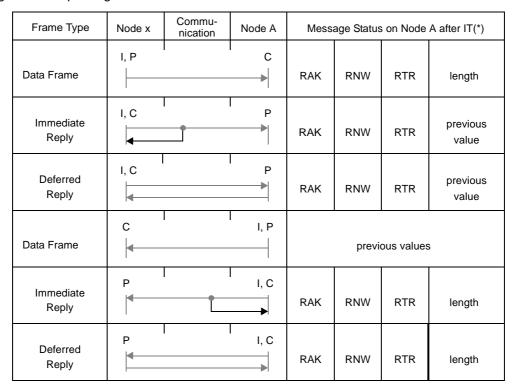

Figure 29. Message Status Updating

P: Producer

I: Initiator

C: Consumer

(\*) After IT ROK or RNOK. In case of IT RE, the values can be erroneous.

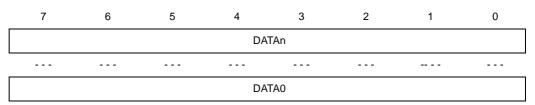

## Message Data (string pointed by: Message Pointer Register + 1)

**DATA0** is the first received (or transmitted) byte, **DATAn** is the last one.

Note:

- 1. If the length reserved (in the message length and status register) for an incoming frame is 2 bytes greater or more, the TSS463AA will write the 2 bytes of the CRC field in the message string just after DATAn.

- Because the VAN frame does not content a message length, the only way for the component to know the length of the DATA field is either the message length register value, either the EOD field detection. When the reserved length is too large, at the moment when it detects the EOD, the TSS463AA has already written the 2 bytes of the CRC field, considering these bytes as normal DATA.

- 2. The Mailbox RAM area is a circular buffer. The next location after 0xFF is 0x80.

#### **Message Types**

There are 5 basic message types defined in the TSS463AA. Two of them (transmit and receive message types) correspond to the normal frame, and the rest correspond to the different versions of reply frames.

| Transmit Message                  |   |   |   |            |  |  |  |  |

|-----------------------------------|---|---|---|------------|--|--|--|--|

| RNW RTR CHTx CHRx                 |   |   |   |            |  |  |  |  |

| Initial setup                     | 0 | 0 | 0 | Don't care |  |  |  |  |

| After transmission 0 0 1 Unchange |   |   |   |            |  |  |  |  |

To transmit a normal data frame on the VAN bus, the user must program an identifier as a Transmit Message. The TSS463AA will then transmit this message on the bus until it has succeeded or the retry count is exceeded.

| Receive Message    |                                    |   |            |   |  |  |  |  |

|--------------------|------------------------------------|---|------------|---|--|--|--|--|

| RNW RTR CHTx CHRx  |                                    |   |            |   |  |  |  |  |

| Initial setup      | 0                                  | 1 | Don't care | 0 |  |  |  |  |

| After transmission | After transmission 0 1 Unchanged 1 |   |            |   |  |  |  |  |

The opposite of the transmit message type is the Receive Message type. This message type will not generate any frames on the bus. Instead it will listen to the bus until a frame passes that matches its identifier, with the mask taken into account, and then receive the data in that frame.

The data received will be stored in the message buffer and the length of the message received is stored in the first byte of the message buffer.

The actual identifier received is stored in the identifier register itself. This identifier may differ from the identifier specified in the register due to the effect of the mask register.

Normally this should not interfere with the next identifier comparison since the bits that may differ are masked via the mask register.

| Reply Request Message                     |   |   |   |   |  |  |  |  |  |

|-------------------------------------------|---|---|---|---|--|--|--|--|--|

| RNW RTR CHTx CHRx                         |   |   |   |   |  |  |  |  |  |

| Initial setup                             | 1 | 1 | 0 | 0 |  |  |  |  |  |

| After transmission<br>(Waiting for reply) | 1 | 1 | 1 | 0 |  |  |  |  |  |

| After reception (of reply)                | 1 | 1 | 1 | 1 |  |  |  |  |  |

The Reply Request Message type is a demand to transmit on the VAN bus a reply request. When this message type is programmed, three things can happen.